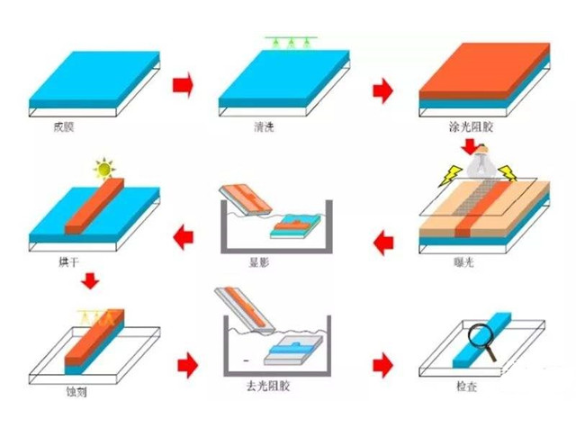

随着半导体技术的不断发展,对光刻图形精度的要求将越来越高。为了满足这一需求,光刻技术将不断突破和创新。例如,通过引入更先进的光源和光学元件、开发更高性能的光刻胶和掩模材料、优化光刻工艺参数等方法,可以进一步提高光刻图形的精度和稳定性。同时,随着人工智能和机器学习等技术的不断发展,未来还可以利用这些技术来优化光刻过程,实现更加智能化的图形精度控制。例如,通过利用机器学习算法对光刻过程中的各项参数进行预测和优化,可以进一步提高光刻图形的精度和一致性。光刻技术不断进化,向着更高集成度和更低功耗迈进。广州图形光刻

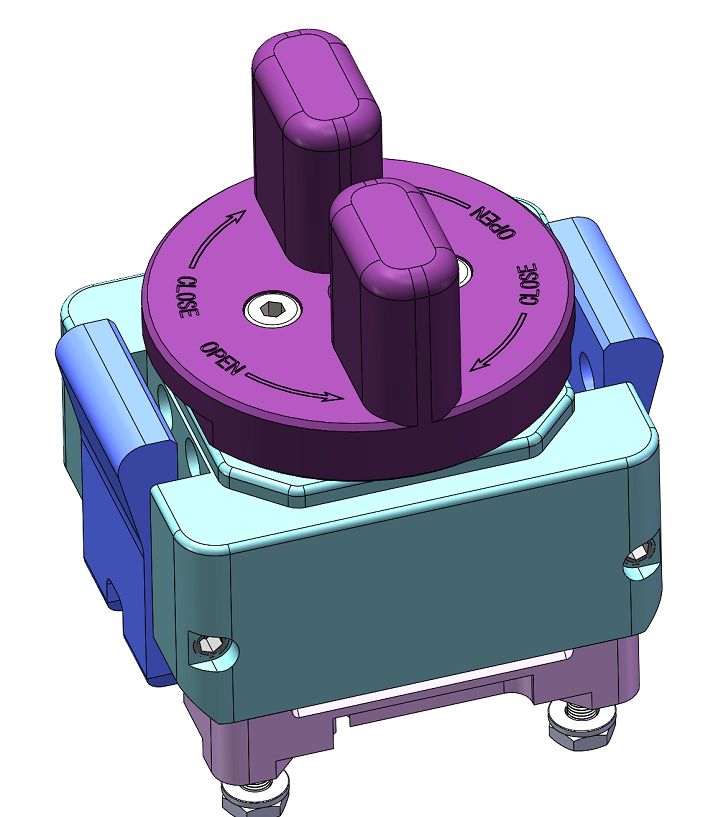

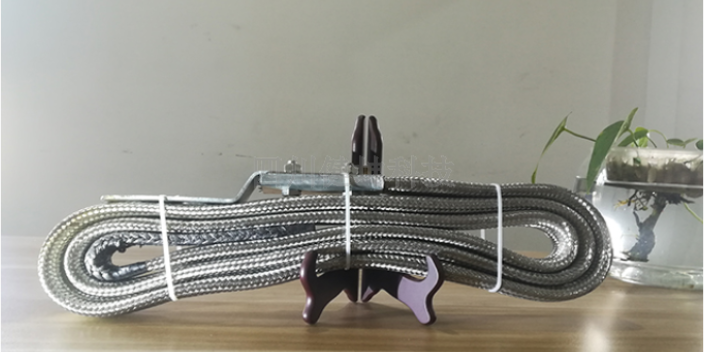

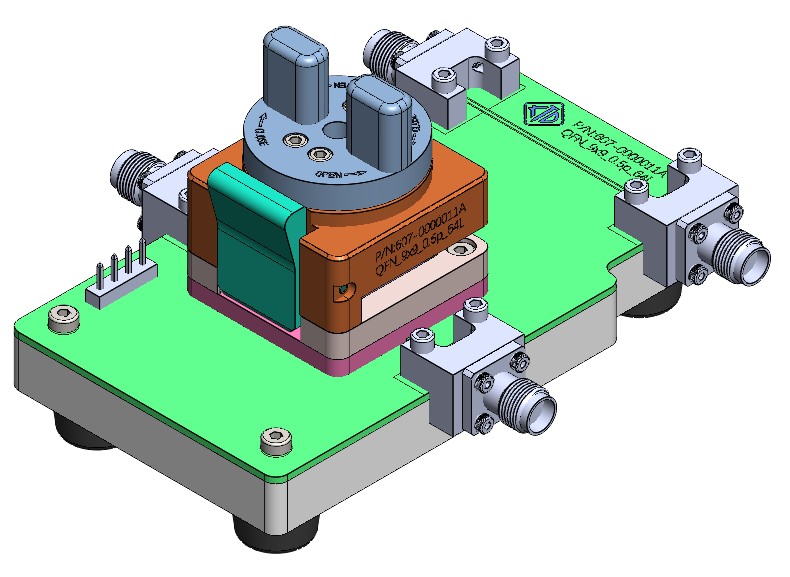

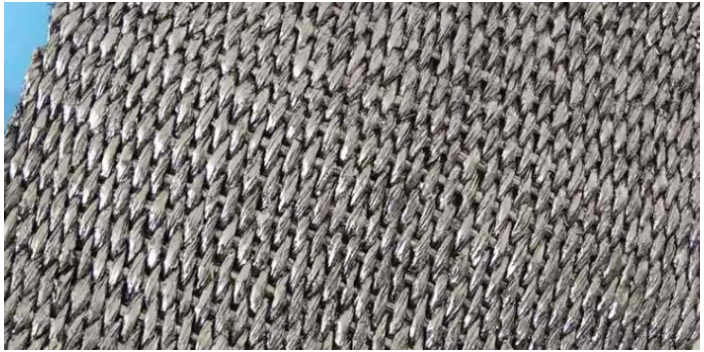

为了确保高精度和长期稳定性,光刻设备的机械结构通常采用高质量的材料制造,如不锈钢、钛合金等,这些材料具有强度高、高刚性和良好的抗腐蚀性,能够有效抵抗外部环境的干扰和内部应力的影响。除了材料选择外,机械结构的合理设计也是保障光刻设备精度和稳定性的关键。光刻设备的各个组件需要精确配合,以减少机械振动和不稳定因素的影响。例如,光刻机的平台、臂杆等关键组件采用精密加工技术制造,确保其在高速移动和定位过程中保持极高的精度和稳定性。此外,通过优化组件的结构设计,如采用轻量化材料和加强筋结构,可以进一步降低机械振动,提高设备的整体性能。广州图形光刻光刻技术对于提升芯片速度、降低功耗具有关键作用。

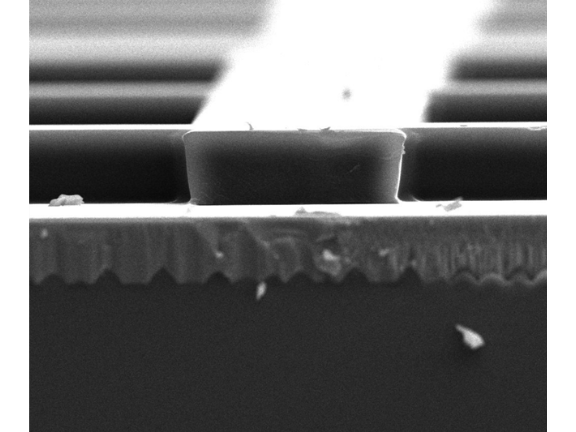

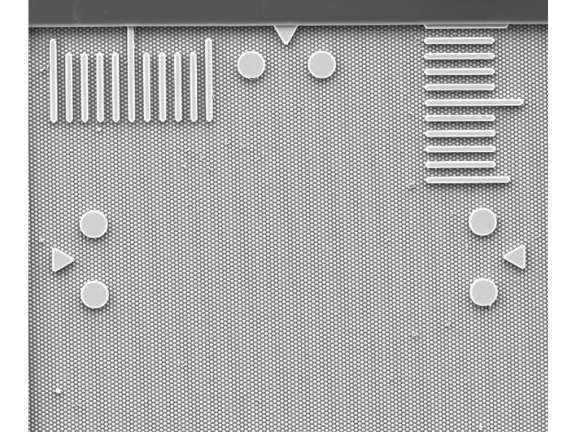

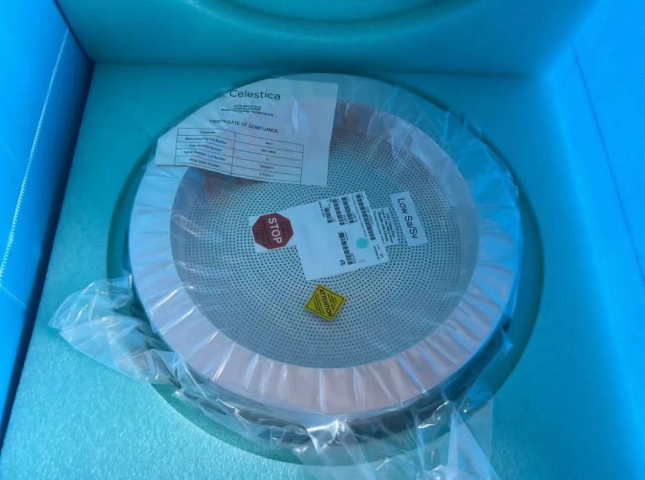

光源稳定性是影响光刻图形精度的关键因素之一。在光刻过程中,光源的不稳定会导致曝光剂量不一致,从而影响图形的对准精度和终端质量。因此,在进行光刻之前,必须对光源进行严格的检查和调整,确保其稳定性。现代光刻机通常采用先进的光源控制系统,能够实时监测和调整光源的强度和稳定性,以确保高精度的曝光。掩模是光刻过程中的另一个关键因素。掩模上的电路图案将直接决定硅片上形成的图形。如果掩模存在损伤、污染或偏差,都会对光刻图形的形成产生严重影响,从而降低图形的精度。因此,在进行光刻之前,必须对掩模进行严格的检查和处理,确保其质量符合要求。此外,随着芯片特征尺寸的不断缩小,对掩模的制造精度和稳定性也提出了更高的要求。

对准与校准是光刻过程中确保图形精度的关键步骤。现代光刻机通常配备先进的对准和校准系统,能够在拼接过程中进行精确调整。通过定期校准系统中的电子光束和样品台,可以减少拼接误差。此外,使用更小的写场和增加写场的重叠区域也可以减轻拼接处的误差。这些技术共同确保了光刻过程中图形的精确对准和拼接。随着科技的不断发展,光刻技术将不断突破和创新,为半导体产业的持续发展注入新的活力。同时,我们也期待光刻技术在未来能够不断突破物理极限,实现更高的分辨率和更小的特征尺寸,为人类社会带来更加先进、高效的电子产品。光刻步骤中的曝光时间需精确到纳秒级。

光刻过程对环境条件非常敏感。温度波动、电磁干扰等因素都可能影响光刻图案的分辨率。因此,在进行光刻之前,必须对工作环境进行严格的控制。首先,需要确保光刻设备的工作环境温度稳定。温度波动会导致光刻胶的膨胀和收缩,从而影响图案的精度。因此,需要安装温度控制系统,实时监测和调整光刻设备的工作环境温度。其次,需要减少电磁干扰。电磁干扰会影响光刻设备的稳定性和精度。因此,需要采取屏蔽措施,减少电磁干扰对光刻过程的影响。此外,还需要对光刻过程中的各项环境参数进行实时监测和调整,以确保其稳定性和一致性。例如,需要监测光刻设备内部的湿度、气压等参数,并根据需要进行调整。实时监控和反馈系统优化了光刻工艺的稳定性。广州图形光刻

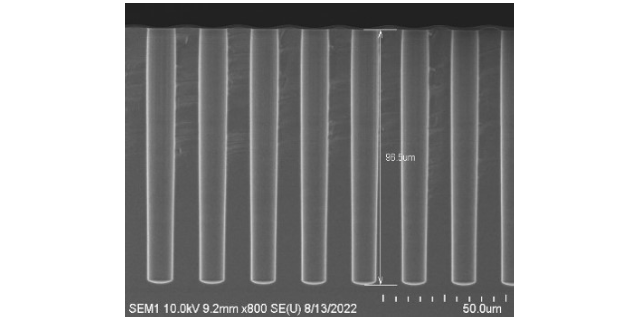

3D光刻技术为半导体封装开辟了新路径。广州图形光刻

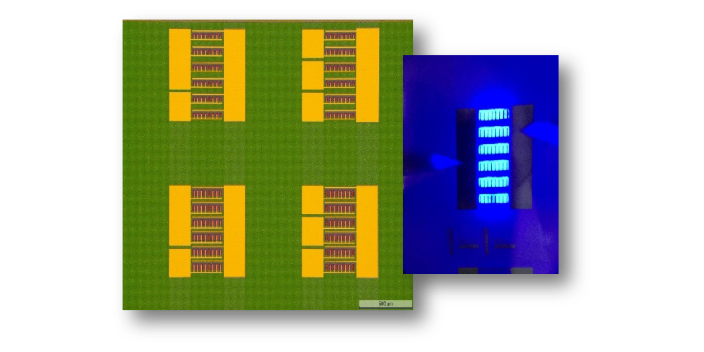

随着特征尺寸逐渐逼近物理极限,传统的DUV光刻技术难以继续提高分辨率。为了解决这个问题,20世纪90年代开始研发极紫外光刻(EUV)。EUV光刻使用波长只为13.5纳米的极紫外光,这种短波长的光源能够实现更小的特征尺寸(约10纳米甚至更小)。然而,EUV光刻的实现面临着一系列挑战,如光源功率、掩膜制造、光学系统的精度等。经过多年的研究和投资,ASML公司在2010年代率先实现了EUV光刻的商业化应用,使得芯片制造跨入了5纳米以下的工艺节点。随着集成电路的发展,先进封装技术如3D封装、系统级封装等逐渐成为主流。光刻工艺在先进封装中发挥着重要作用,能够实现微细结构的制造和精确定位。这对于提高封装密度和可靠性至关重要。广州图形光刻

文章来源地址: http://dzyqj.shopjgsb.chanpin818.com/dzcllbjjgj/bdtcl/deta_27143946.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3